# SP720 Series 3pF 4kV Diode Array

#### **Pinout**

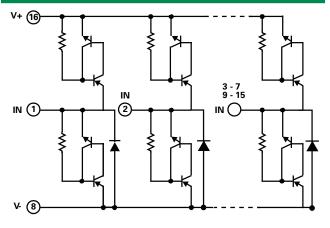

## **Functional Block Diagram**

#### **Description**

The SP720 is an array of SCR/Diode bipolar structures for ESD and over-voltage protection to sensitive input circuits. The SP720 has 2 protection SCR/Diode device structures per input. A total of 14 available inputs can be used to protect up to 14 external signal or bus lines. Over-voltage protection is from the IN (pins 1-7 and 9-15) to V+ or V-.

The SCR structures are designed for fast triggering at a threshold of one +V $_{\rm BE}$  diode threshold above V+ (Pin 16) or a -V $_{\rm BE}$  diode threshold below V- (Pin 8). From an IN input, a clamp to V+ is activated if a transient pulse causes the input to be increased to a voltage level greater than one V $_{\rm BE}$  above V+. A similar clamp to V- is activated if a negative pulse, one V $_{\rm BE}$  less than V-, is applied to an IN input. Standard ESD Human Body Model (HBM) Capability is:

#### **Features**

| ESD Interface Capability for HBM Standards                      |

|-----------------------------------------------------------------|

| - MIL STD 3015.715kV                                            |

| - IEC 61000-4-2, Direct Discharge,                              |

| - Single Input                                                  |

| -Two Inputs in Parallel 8kV (Level 4)                           |

| - IEC 61000-4-2, Air Discharge15kV (Level 4)                    |

| High Peak Current Capability                                    |

| - IEC 61000-4-5 (8/20µs)±3A                                     |

| - Single Pulse, 100µs Pulse Width ±2A                           |

| - Single Pulse, 4µs Pulse Width±5A                              |

| <ul> <li>Designed to Provide Over-Voltage Protection</li> </ul> |

| - Single-Ended Voltage Range to+30V                             |

| - Differential Voltage Range to±15V                             |

| • Fast Switching2ns Risetime                                    |

| • Low Input Leakages1nA at 25° (Typ)                            |

| • Low Input Capacitance                                         |

| An Array of 14 SCR/Diode Pairs                                  |

| • Operating Temperature Range40°C to 105°C                      |

## **Applications**

- Microprocessor/Logic Input Protection

- Data Bus Protection

- Analog Device Input Protection

- Voltage Clamp

Life Support Note:

#### Not Intended for Use in Life Support or Life Saving Applications

The products shown herein are not designed for use in life sustaining or life saving applications unless otherwise expressly indicated.

## TVS Diode Arrays (SPA™ Family of Products)

General Purpose ESD Protection - SP720 Series

### **Absolute Maximum Ratings**

| Parameter                                                                                    | Rating    | Units |

|----------------------------------------------------------------------------------------------|-----------|-------|

| Continuous Supply Voltage, (V+) - (V-)                                                       | +35       | V     |

| Forward Peak Current, $I_{\rm IN}$ to $V_{\rm CC}$ , $I_{\rm IN}$ to GND (Refer to Figure 5) | ±2, 100μs | А     |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

Note:

ESD Ratings and Capability - See Figure 1, Table 1 Load Dump and Reverse Battery (Note 2)

| Thermal Information                                                  |               |       |

|----------------------------------------------------------------------|---------------|-------|

| Parameter                                                            | Rating        | Units |

| Thermal Resistance (Typical, Note 1)                                 | $\theta_{JA}$ | °C/W  |

| PDIP Package                                                         | 90            | °C/W  |

| SOIC Package                                                         | 130           | °C/W  |

| Maximum Storage Temperature Range                                    | -65 to 150    | °C    |

| Maximum Junction Temperature (Plastic Package)                       | 150           | °C    |

| Maximum Lead Temperature<br>(Soldering 20-40s) (SOIC Lead Tips Only) | 260           | °C    |

<sup>1.</sup>  $\theta_{\text{\tiny LA}}$  is measured with the component mounted on an evaluation PC board in free air.

## Electrical Characteristics $T_{\Delta} = -40^{\circ}\text{C}$ to $105^{\circ}\text{C}$ , $V_{\text{IN}} = 0.5V_{\text{CC}}$ , Unless Otherwise Specified

| Parameter                                                | Symbol              | Test Conditions                             | Min | Тур     | Max | Units |

|----------------------------------------------------------|---------------------|---------------------------------------------|-----|---------|-----|-------|

| Operating Voltage Range,<br>$V_{SUPPLY} = [(V+) - (V-)]$ | V <sub>SUPPLY</sub> |                                             | -   | 2 to 30 | -   | V     |

| Forward Voltage Drop:                                    |                     | I <sub>IN</sub> = 1A (Peak Pulse)           |     |         |     |       |

| IN to V-                                                 | V <sub>FWDL</sub>   |                                             | -   | 2       | -   | V     |

| IN to V+                                                 | V <sub>FWDH</sub>   |                                             | -   | 2       | -   | V     |

| Input Leakage Current                                    | I <sub>IN</sub>     |                                             | -20 | 5       | 20  | nA    |

| Quiescent Supply Current                                 | QUIESCENT           |                                             | -   | 50      | 200 | nA    |

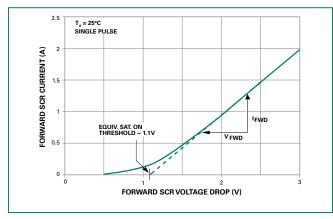

| Equivalent SCR ON Threshold                              |                     | Note 3                                      | -   | 1.1     | -   | V     |

| Equivalent SCR ON Resistance                             |                     | V <sub>FWD</sub> /I <sub>FWD</sub> ; Note 3 | -   | 1       | -   | Ω     |

| Input Capacitance                                        | C <sub>IN</sub>     |                                             | -   | 3       | -   | pF    |

| Input Switching Speed                                    | t <sub>on</sub>     |                                             | -   | 2       | -   | ns    |

#### Notes:

- 2. In automotive and battery operated systems, the power supply lines should be externally protected for load dump and everse battery V+ and V- pins are connected to the same supply voltage source as the device or control line under protection, a current limiting resistor should be connected in series between the external supply and the SP720 supply pins to limit reverse battery current to within the rated maximum limits. Bypass capacitors of typically 0.01µF or larger from the V+ and V- pins to ground are recommended.

- 3. Refer to the Figure 3 graph for definitions of equivalent "SCR ON Threshold" and "SCR ON Resistance." These characteristics are given here for thumb-rule nformation to determine peak current and dissipation under EOS conditions.

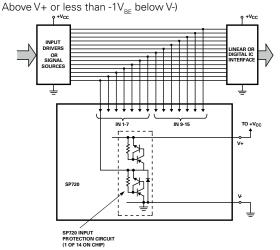

## **Typical Application of the SP720**

(Application as an Input Clamp for Over-voltage, greater than  $1V_{BE}$

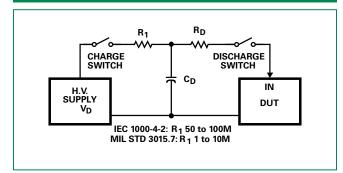

#### **ESD Capability**

ESD capability is dependent on the application and defined test standard. The evaluation results for various test standards and methods based on Figure 1 are shown in Table 1.

For the "Modified" MIL-STD-3015.7 condition that is defined as an "in-circuit" method of ESD testing, the V+ and V- pins have a return path to ground and the SP720 ESD capability is typically greater than 15kV from 100pF through 1.5k $\Omega$ . By strict definition of MIL-STD-3015.7 using "pin-to-pin" device testing, the ESD voltage capability is greater than 6kV. The MIL-STD-3015.7 results were determined from AT&T ESD Test Lab measurements.

The HBM capability to the IEC 61000-4-2 standard is greater than 15kV for air discharge (Level 4) and greater than 4kV for direct discharge (Level 2). Dual pin capability (2 adjacent pins in parallel) is well in excess of 8kV (Level 4).

For ESD testing of the SP720 to EIAJ IC121 Machine Model (MM) standard, the results are typically better than 1kV from 200pF with no series resistance.

Figure 1: Electrostatic Discharge Test

**Table 1: ESD Test Conditions**

| Standard        | Type/Mode                                         | $R_{_{\mathrm{D}}}$ | C <sub>D</sub> | $\pm V_{_{\mathrm{D}}}$ |

|-----------------|---------------------------------------------------|---------------------|----------------|-------------------------|

| MIL STD 3015.7  | Modified HBM                                      | 1.5kΩ               | 100pF          | 15kV                    |

| WIIL 31D 3015.7 | Standard HBM                                      | 1.5kΩ               | 100pF          | 6kV                     |

|                 | HBM, Air Discharge                                | 330Ω                | 150pF          | 15kV                    |

| IEC 61000-4-2   | HBM, Direct Discharge                             | 330Ω                | 150pF          | 4kV                     |

|                 | HBM, Direct Discharge,<br>Two Parallel Input Pins | 330Ω                | 150pF          | 8kV                     |

| EIAJ IC121      | Machine Model                                     | 0kΩ                 | 200pF          | 1kV                     |

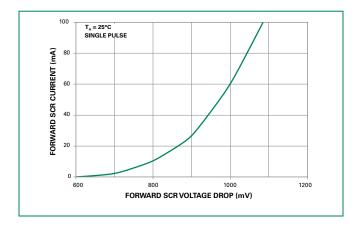

Figure 2: Low Current SCR Forward Voltage Drop Curve

Figure 3: High Current SCR Forward Voltage Drop Curve

General Purpose ESD Protection - SP720 Series

### **Peak Transient Current Capability for Long Duration Surges**

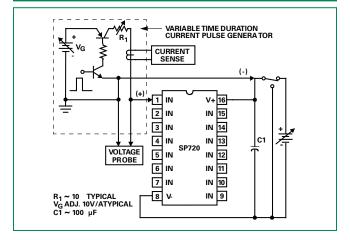

The peak transient current capability rises sharply as the width of the current pulse narrows. Destructive testing was done to fully evaluate the SP720's ability to withstand a wide range of transient current pulses. The circuit used to generate current pulses is shown in Figure 4.

The test circuit of Figure 4 is shown with a positive pulse input. For a negative pulse input, the (-) current pulse input goes to an SP720 'IN' input pin and the (+) current pulse input goes to the SP720 V- pin. The V+ to V- supply of the SP720 must be allowed to float. (i.e., It is not tied to the ground reference of the current pulse generator.) Figure 5 shows the point of overstress as defined by increased leakage in excess of the data sheet published limits.

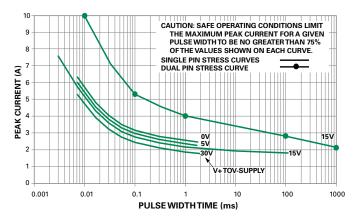

The maximum peak input current capability is dependent on the V+ to V- voltage supply level, improving as the supply voltage is reduced. Values of 0, 5, 15 and 30 voltages are shown. The safe operating range of the transient peak current should be limited to no more than 75% of the measured overstress level for any given pulse width as shown in Figure 5.

When adjacent input pins are paralleled, the sustained peak current capability is increased to nearly twice that of a single pin. For comparison, tests were run using dual pin combinations 1+2, 3+4, 5+6, 7+9, 10+11, 12+13 and 14+15.

The overstress curve is shown in Figure 5 for a 15V supply condition. The dual pins are capable of 10A peak current for a 10µs pulse and 4A peak current for a 1ms pulse. The complete for single pulse peak current vs. pulse width time ranging up to 1 second are shown in Figure 5.

Figure 4: Typical SP720 Peak Current Test Circuit with a Variable Pulse Width Input

Figure 5: SP720 Typical Nonrepetitive Peak Current

Pulse Capability

Showing the Measured Point of Overstress in Amperes vs pulse width time in milliseconds ( $T_{\Delta}=25^{\circ}C$ )

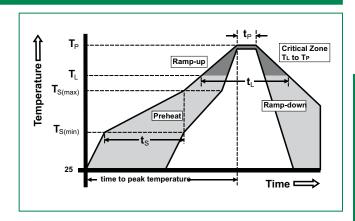

#### **Soldering Parameters**

| Reflow Co                                       | ndition                                        | Pb – Free assembly      |

|-------------------------------------------------|------------------------------------------------|-------------------------|

|                                                 | -Temperature Min (T <sub>s(min)</sub> )        | 150°C                   |

| Pre Heat                                        | -Temperature Max (T <sub>s(max)</sub> )        | 200°C                   |

|                                                 | -Time (min to max) (t <sub>s</sub> )           | 60 – 180 secs           |

| Average ra                                      | amp up rate (Liquidus) Temp<br>k               | 5°C/second max          |

| T <sub>S(max)</sub> to T <sub>L</sub>           | - Ramp-up Rate                                 | 5°C/second max          |

| Reflow                                          | -Temperature (T <sub>L</sub> ) (Liquidus)      | 217°C                   |

| nellow                                          | -Temperature (t <sub>L</sub> )                 | 60 – 150 seconds        |

| PeakTemp                                        | erature (T <sub>P</sub> )                      | 260 <sup>+0/-5</sup> °C |

| Time with<br>Temperate                          | in 5°C of actual peak<br>ure (t <sub>p</sub> ) | 20 – 40 seconds         |

| Ramp-dov                                        | vn Rate                                        | 5°C/second max          |

| Time 25°C to peak Temperature (T <sub>P</sub> ) |                                                | 8 minutes Max.          |

| Do not exc                                      | ceed                                           | 260°C                   |

|                                                 |                                                |                         |

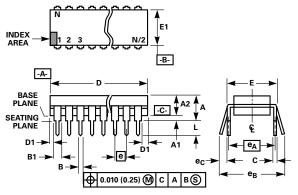

## Package Dimensions Dual-In-Line Plastic Packages (PDIP)

#### Notes:

- Controlling Dimensions: INCH. in case of conflict between English and Metric dimensions, the inch dimensions control.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication No. 95.

- 4. Dimensions A, A1 and L are measured with the package seated in JE-DEC seating plane gauge GS-3.

- D, D1, and E1 dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010 inch (0.25mm).

- 6. E and  $e_A$  are measured with the leads constrained to be perpendicular to datum -C-.

- 7.  $e_{_{B}}$  and  $e_{_{C}}$  are measured at the lead tips with the leads unconstrained.  $e_{_{C}}$  must be zero or greater.

- 8. B1 maximum dimensions do not include dambar protrusions. Dambar protrusions shall not exceed 0.010 inch (0.25mm).

- 9. N is the maximum number of terminal positions.

- 10. Corner leads (1, N, N/2 and N/2 + 1) for E8.3, E16.3, E18.3, E28.3, E42.6 will have a B1 dimension of 0.030 0.045 inch (0.76 1.14mm).

| Package        | PDIP                 |       |           |       |       |

|----------------|----------------------|-------|-----------|-------|-------|

| Pins           | 16 Lead Dual-in-Line |       |           |       |       |

| JEDEC          | MS-001               |       |           |       |       |

|                | Millime              | eters | Inch      | ies   | Natas |

|                | Min                  | Max   | Min       | Max   | Notes |

| Α              | -                    | 5.33  | -         | 0.210 | 4     |

| A1             | 0.39                 | -     | 0.015     | -     | 4     |

| A2             | 2.93                 | 4.95  | 0.115     | 0.195 | -     |

| В              | 0.356                | 0.558 | 0.014     | 0.022 | -     |

| B1             | 1.15                 | 1.77  | 0.045     | 0.070 | 8, 10 |

| С              | 0.204                | 0.355 | 0.008     | 0.014 | -     |

| D              | 18.66                | 19.68 | 0.735     | 0.775 | 5     |

| D1             | 0.13                 | -     | 0.005     | -     | 5     |

| E              | 7.62                 | 8.25  | 0.300     | 0.325 | 6     |

| E1             | 6.10                 | 7.11  | 0.240     | 0.280 | 5     |

| е              | 2.54 BSC             |       | 0.100     | BSC   | -     |

| e <sub>A</sub> | 7.62 BSC             |       | 0.300 BSC |       | 6     |

| e <sub>B</sub> | -                    | 10.92 | -         | 0.430 | 7     |

| L              | 2.93                 | 3.81  | 0.115     | 0.150 | 4     |

| N              | 16 16                |       |           | 9     |       |

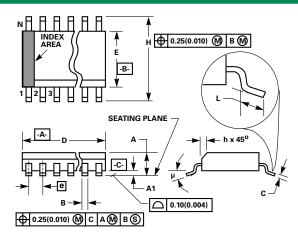

## Package Dimensions — Small Outline Plastic Packages (SOIC)

#### Notes

- Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication Number 95.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- 3. Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- 4. Dimension "E" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

- The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 6. "L" is the length of terminal for soldering to a substrate.

- 7. "N" is the number of terminal positions.

- 8. Terminal numbers are shown for reference only.

- 9. The lead width "B", as measured 0.36mm (0.014 inch) or greater above the seating plane, shall not exceed a maximum value of 0.61mm (0.024 inch).

- Controlling dimension:MILLIMETER. Converted inch dimensions are not necessarily exact.

| Package | SOIC     |       |        |        |       |  |

|---------|----------|-------|--------|--------|-------|--|

| Pins    |          | 16    |        |        |       |  |

| JEDEC   | MS-012   |       |        |        |       |  |

|         | Millim   | eters | Inch   | ies    | Nista |  |

|         | Min      | Max   | Min    | Max    | Notes |  |

| Α       | 1.35     | 1.75  | 0.0532 | 0.0688 | -     |  |

| A1      | 0.10     | 0.25  | 0.0040 | 0.0098 | -     |  |

| В       | 0.33     | 0.51  | 0.013  | 0.020  | 9     |  |

| С       | 0.19     | 0.25  | 0.0075 | 0.0098 | -     |  |

| D       | 9.80     | 10.00 | 0.3859 | 0.3937 | 3     |  |

| E       | 3.80     | 4.00  | 0.1497 | 0.1574 | 4     |  |

| е       | 1.27 BSC |       | 0.050  | BSC    | -     |  |

| Н       | 5.80     | 6.20  | 0.2284 | 0.2440 | -     |  |

| h       | 0.25     | 0.50  | 0.0099 | 0.0196 | 5     |  |

| L       | 0.40     | 1.27  | 0.016  | 0.050  | 6     |  |

| N       | 16       | 3 16  |        | 7      |       |  |

| μ       | 0°       | 8°    | 0°     | 8°     | -     |  |

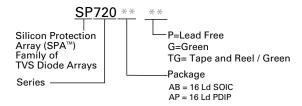

## **Part Numbering System**

See Ordering Information section for specific options available

## **Product Characteristics**

| Lead Plating        | Matte Tin              |

|---------------------|------------------------|

| Lead Material       | Copper Alloy           |

| Lead Coplanarity    | 0.004 inches (0.102mm) |

| Substitute Material | Silicon                |

| Body Material       | Molded Epoxy           |

| Flammability        | UL 94 V-0              |

## **Ordering Information**

| Part Number | Temp. Range (°C) | Package                     | Environmental<br>Informaton | Marking                 | Min. Order |

|-------------|------------------|-----------------------------|-----------------------------|-------------------------|------------|

| SP720APP    | -40 to 105       | 16 Ld PDIP                  | Lead-free                   | SP720AP(P) <sup>1</sup> | 1500       |

| SP720ABG    | -40 to 105       | 16 Ld SOIC                  | Green                       | SP720A(B)G <sup>2</sup> | 1920       |

| SP720ABTG   | -40 to 105       | 16 Ld SOIC<br>Tape and Reel | Green                       | SP720A(B)G <sup>2</sup> | 2500       |

#### Notes:

- 1. SP720AP(P) means device marking either SP720AP or SP720APP.

- $2.\ SP720A(B)G\ means\ device\ marking\ either\ SP720AG\ or\ SP720ABG\ which\ are\ good\ for\ types\ SP720ABG\ and\ SP720ABTG.$